Paralelna obrada

Paralelna obrada je postupak kod kojega se više instrukcija obrađuje istovremeno.[1] Obrada se zasniva na principu da se veliki problemi gotovo uvijek mogu podijeliti na manje te onda obraditi istovremeno (paralelno). Ovaj tip obrade postoji u nekoliko oblika:

- 1. Paralelizam na razini bita,

- 2. Paralelizam na razini instrukcije,

- 3. Podatkovni paralelizam,

- 4. Zadaćni paralelizam (engl. task parallelism).

Navedeni oblik obrade je korišten dugo vremena u procesiranju visoke brzine, ali interes je ovih godina jako porastao zbog fizičkih ograničenja koja sprječavaju frekvencijsko skaliranje. U posljednje vrijeme paralelna obrada je postala vodeća paradigma u računalnim arhitekturama, najvećim djelom u obliku višejezgrenih procesora.[2] Ipak je potrošnja u paralelnim računalima postala zabrinjavajuća.[3]

Paralelne računalne programe je mnogo teže razvijati nego sekvencijalne[4] zato što istodobnost uvodi nekoliko novih klasa potencijalnih softverskih bugova od kojih su „race condition“ najčešći. Komunikacija i sinkronizacija između različitih podzadataka je jedno od najvećih ograničenja za dobivanje dobrih performansi paralelnog programa. Ubrzanje izvršavanja programa kao rezultat paralelne obrade je opisano Amdahlovim zakonom.

Pozadina

Uobičajeno se programska podrška piše za serijsku obradu. Rješenje problema nalazi se u kreiranju algoritma koji proizvodi serijski niz instrukcija. Ove instrukcije se izvršavaju na centralnom procesoru jednog računala. Samo jedna instrukcija se može izvršiti u jednom periodu vremena, a nakon njenog izvršenja sljedeća.[5]

Nasuprot tome paralelna obrada koristi simultano više paralelnih elemenata kako bi riješila problem. To je postignuto podjelom problema u dijelove koji su neovisni pa svaki element obrade može izvršiti jedan dio vlastitog algoritma istovremeno s drugima. Elementi obrade su različiti i uključuju resurse kao što su računala s više procesora, mreža računala, specijalizirani hardver ili bilo koja kombinacija navedenog.[5]

Frekvencijsko skaliranje je bilo glavni uzrok rasta računalnih performansi od sredine 1980-ih do 2004. godine. Vrijeme izvođenja programa je jednako broju instrukcija, pomnoženom sa srednjim vremenom izvršenja po instrukciji. Održavajući sve ostalo konstantnim, povećanjem frekvencije smanjuje se srednje vrijeme izvršavanja po instrukciji. Iz toga razloga, povećanjem frekvencije se smanjuje vrijeme izvođenja svih računski zahtjevnih programa.[6]

Potrošnja energije u čipu je dana izrazom:

gdje je P snaga, C - kapacitivnost uključenja po ciklusu takta (proporcionalna broju tranzistora čiji se ulazi mijenjaju), V - napon i F - frekvencija procesora.[7]

Povećanje frekvencije utječe na snagu koju procesor koristi. Povećana potrošnje energije procesora je dovelo do prekida razvoja Intelovih Tejas i Jayhawk procesora, što se povezuje s krajem frekvencijskog skaliranja kao dominantne paradigme računale arhitekture.[8]

Mooreov zakon je empirijsko opažanje koje opisuje udvostručavanje gustoće tranzistora u mikroprocesoru u periodu od 18 do 24 mjeseci. Usprkos problemima sa disipacijom i ponavljanim predviđanjima kraja, Mooreov zakon još uvijek vrijedi. S krajem frekvencijskog skaliranja, dodatni tranzistori (koji se više ne koriste za frekvencijsko skaliranje) se mogu iskoristiti kako bi dodali hardver potreban za paralelnu obradu.

Amdahlov i Gustafsonov zakon

Teoretski gledano, ubrzanje dobiveno paralelizacijom udvostručenjem elemenata za obradu trebalo bi prepoloviti vrijeme izvođenja, a drugim udvostručenjem također bi se vrijeme izvođenja trebalo prepoloviti. Ipak, vrlo mali broj paralelnih algoritama postiže optimalno ubrzanje. Većina ima skoro pa linearno ubrzanje za mali broj elemenata za obradu. Daljnjim povećanjem broja elemenata za obradu vrijeme obrade postaje jednoliko (konstantno).

Performanse algoritma u platformama s paralelnom obradom ovise o paraleliziranosti algoritma u cilju dostizanja performansi, stoga je važno pripaziti na Amdahlov zakon. Amdahlov zakon je formulirao Gene Amdahl 60-ih godina 20. stoljeća.[9] On tvrdi da mali dijelovi programa koji se ne mogu paralelizirati ograničavaju ukupno ubrzanje dobiveno paralelizacijom. Bilo koji matematički ili inženjerski problem uobičajeno će se sastojati od nekoliko dijelova, koji se mogu paralelizirati i nekoliko koji se ne mogu paralelizirati (sekvencijalne komponente). Ovaj odnos je dan izrazom:

gdje je S ubrzanje programa (kao faktor njegovog osnovnog sekvencijalnog izvođenja), a P dio koji se paralelizira. Ne može se ostvariti ubrzanje više od 10x, ako sekvencijalni dio programa iznosi 10% izvođenja, bez obzira koliko procesora dodajemo. Na ovaj način je postavljena gornja granica korisnosti dodavanja više paralelnih izvršnih jedinica."[10]

Gustafsonov zakon je drugi zakon računalnog inženjeringa, usko vezan za Amdahlov zakon. Gustafsonov zakon se može formulirati kao:

gdje je P - broj procesora, S - ubrzanje, i α - neparalelizirani dijelovi procesa.[11] Amdahlov zakon pretpostavlja konačnu veličinu problema i ta veličina sekvencijalnog dijela je neovisna o broju procesora, dok Gustafsonov zakon nema tih pretpostavki.

Ovisnosti

Razumijevanje podatkovnih ovisnosti je jedan od osnova shvaćanja implementacije paralelnih algoritama. Niti jedan program se ne može izvesti brže od najdužeg lanca ovisnih izračuna (kritični put) zbog činjenice da izračuni koji su ovisni, a uvode slijed izvršavanja. Na sreću, većina algoritama se ne sastoji od dugačkih lanaca, međusobno ovisnih izračuna i uvijek postoje mnoge mogućnosti paralelnog izvršavanja neovisnih izračuna.

Neka su Pi i Pj dva fragmenta programa. Bernsteinovi uvjeti[12] opisuju stanje kada su dva fragmenta neovisna i mogu biti paralelno izvršeni. Neka su Ii sve ulazne varijable od Pi i Oi - izlazne varijable.

Analogno tome Pj. Pi i Pj su neovisne ako zadovoljavaju uvjete:

Narušavanjem prvog uvjeta uvodi se ovisnost toka, što znači da prvi izraz daje rezultat koji koristi drugi izraz. Drugi uvjet predstavlja protuovisnost, kad prvi iskaz prepisuje varijablu koju koristi drugi izraz. Zadnji uvjet q je ovisnost izlaza. Kad dvije varijable zapisuju na istu lokaciju, konačni izlaz mora biti iz drugog iskaza.[13]

Na primjer, pretpostavi se sljedeća funkcija:

1: function Dep(a,b) 2: c := a*b 3: d := 2*c 4: end function

Operacija u trećoj liniji koda funkcije Dep(a,b) ne može se izvršiti prije (ili čak paralelno) druge operacije zbog činjenice da treća operacija koristi rezultat iz druge. Navedeno krši prvi uvjet i tako ubacuje ovisnost toka.

1: function NoDep(a,b) 2: c := a*b 3: d := 2*b 4: e := a+b 5: end function

U ovom primjeru ne postoje ovisnosti između instrukcija pa se one mogu obraditi paralelno.

Bernsteinov uvjet ne dopušta dijeljenje memorije između različitih procesa, stoga zahtjeva neku od metoda raspodjeljivanja pristupa, kao što su semafori, barijere ili neku drugu sinkronizacijsku metodu.

“Race condition”, međusobno isključivanje, sinkronizacija i paralelno usporavanje

Podzadatke u paralelnim programima često se nazivaju nitima. Neke paralelne računalne arhitekture koriste manje, lakše verzije niti, poznate kao vlakna, dok drugi koriste veće verzije poznate kao procesi. Ipak, „niti“ (engl. threads) se općenito prihvaćaju kao opći nazivi za podzadatke. Niti će često morati obnoviti neke varijable koje međusobno dijele. Instrukcije između dva programa se isprepliću u bilo kojem redoslijedu. Navedeno se može vidjeti na sljedećem primjeru programa.

| Nit A | Nit B |

| 1A: Pročitaj varijablu V | 1B: Pročitaj varijablu V |

| 2A: Povećaj varijablu V za 1 | 2B: Povećaj varijablu V za 1 |

| 3A: Zapiši varijablu V | 3B: Zapiši varijablu V |

Ako je instrukcija 1B izvršena između 1A i 3A ili je instrukcija 1A izvršena između 1B i 3B, program će izračunati pogrešni podatak. Ovo se još naziva i "race condition". Programer mora koristi zaključavanje kako bi pružio međusobna isključivost. Zaključavanje je konstruktor u programskom jeziku koji pruža kontrolu jednooj niti nad varijablom i spriječava druge niti da ih čitaju ili zapisuju dok se varijabla ne oslobodi. Dok nit drži pravo pristupa ona može izvršiti svoj kritični dio (dio programa koji zahtjeva prvenstvo pristupa varijabli)i otključati pristup podatcima kada je završila sa obradom. Ovo garantira ispravno izvođenje programa, gornji program se može ponovno napisati korištenjem zaključavanja.

| Nit A | Nit B |

| 1A: Zaključaj varijablu V | 1B: Zaključaj varijablu V |

| 2A: Pročitaj varijablu V | 2B: Pročitaj varijablu V |

| 3A: Povećaj varijablu V za 1 | 3B: Povećaj varijablu V za 1 |

| 4A: Zapiši varijablu V | 4B: Zapiši varijablu V |

| 5A: Otključaj varijablu V | 5B: Otključaj varijablu V |

Jedna nit će uspješno zaključati varijablu V, dok će druga biti onemogućena – nemoguće ju je proslijediti dok V nije nanovo otključana. Ovo pruža ispravno izvršenje programa. Zaključavanje će istodobno jako usporiti izvođenje programa, dok neophodno osigurava ispravno izvršavanje programa. Zaključavanjem više varijabli korištenjem „non-atomic“ ključeva uvodi se mogućnost da se program završi u potpunom zastoju. „Atomic lock“ je ključ koji odjednom zaključava više varijabli. U slučaju da ne može zaključati sve, tada ne zaključava niti jednu. Ako svaka od dvije niti treba zaključati dvije iste varijable korištenjem „non-atomic“ ključeva, moguće je da će jedan zaključati jednu od njih, dok će drugi zaključati drugu varijablu. U takvom slučaju, niti jedna nit ne može završiti pa se događa potpuni zastoj (engl. deadlock).

Mnogi paralelni programi zahtijevaju da njihovi podzadaci rade sinkrono, što zahtjeva korištenje barijera. Barijere se uobičajeno implementiraju korištenjem softverskog zaključavanja. Jedna klasa algoritama, poznatija kao „lock-free and wait-free algorithms“, izbjegava zajedničko zaključavanje i barijere. Ipak ovaj pristup općenito otežava implementaciju pa zahtijeva ispravno dizajniranje struktura podataka.

Neće svako paraleliziranje rezultirati ubrzanjem. Općenito, kako se zadaci dijele u sve više niti, te niti zahtijevaju sve više vremena za međusobno komuniciranje. Moguće je da dodatna komunikacija dominira vremenom utrošenim za rješavanje problema pa daljnja paralelizacija (koja dijeli preko još više niti) povećava, umjesto da smanji, period vremena koji je potreban za završetak. Opisano je još poznatije kao paralelno usporavanje.

Paralelizam fine zrnatosti, grube zrnatosti i zbunjujući paralelizam

Aplikacije se često svrstavaju prema učestalosti sinkronizacije ili međusobne komunikacije podzadataka. Aplikacija koja je prilagođena paralelizmu fine zrnatosti (engl. fine-grained parallelism) podzadataka koji komuniciraju mnogo puta u sekundi. Druga aplikacija, koja je prilagođena paralelizmu grube zrnatosti (engl. coarse-grained parallelism), ne komunicira mnogo puta u sekundi te zbunjujuća paralelizacija (engl. embarrassingly parallel), ako mora rijetko ili nikada komunicirati. Zbunjujuće paralelne aplikacije se smatraju najjednostavnije za paraleliziranje.

Modeli dosljednosti

Paralelni programski jezici i računala u paralelnom radu moraju imati model dosljednosti (memorijski model). Model dosljednosti definira pravila kako se izvršavaju operacije u računalnoj memoriji i kako se izvodi rezultat.

Jedan od prvih modela dosljednosti je bio Leslie Lamportov model dosljednosti. Sekvencijalna dosljednost je svojstvo paralelnog programa da njegovo paralelno izvođenje dovodi do istog rezultata kao i kod sekvencijalnog programa. Program je sekvencijalno dosljedan ako je zadovoljen sljedeći uvjet: „Rezultat ikojeg izvršavanja je isti kao da su se operacije svih procesora izvele u sekvencijalnom slijedu, i da se operacija svakog pojedinačnog procesora izvela u slijedu određenim programom“.[11]

Softverske memorijske transakcije su čest tip modela slijednosti. Model softverskih memorijskih transakcija uzima koncept „atomic transaction“ iz teorije baza podataka te ga primjenjuje prilikom pristup memoriji.

Ovi modeli se mogu matematički predstaviti na brojne načine. „Process calculus“ je dio matematike koja se bavi istovremenošću. „Process calculus“ se može podijeliti na „ambient calculus“, „calculus of communicating systems“ te komunikaciju sekvencijalnih procesa. Petrijeve mreže su rani pokušaj kodifikacije pravila modela slijednosti. Teorija toka podataka kasnije je izvedena iz Petrijeve mreže. Kasnije je nastala arhitektura toka podataka koja fizički implementira ideje toka podataka.

Flynnova taksonomija

Michael J. Flynn je načinio jednu od najranijih klasifikacija sustava za paralelna i sekvencijalna računala i programe, danas poznatijom kao Flynnova taksonomija. Flynn je klasificirao programe i računala po tome rade li upotrebom jednog ili više seta instrukcija te koriste li instrukcije jedan ili više seta podataka.

| Jedna Instrukcija |

Više Instrukcija | |

|---|---|---|

| Jedan Podatak |

SISD | MISD |

| Više Podataka |

SIMD | MIMD |

Klasa jedna-instrukcija-jedan-podatak (SISD – Single Instruction Single Data) je ekvivalentna potpuno sekvencijalnom programu. Klasa jedna-instrukcija-više-podataka (SIMD – Single Instruction Multiple Data) je analogna izvršavanju iste operacije ponavljanjem kroz velike setove podataka. Opisano se često koristi kod aplikacija za procesiranje signala. Klasa više-instrukcija-jedan-podatak (Multiple Instruction Single Data) je rijetko korištena. Kada se otkriju računalne arhitekture koje tako funkcioniraju (sistolička polja), materijalizirat će se nekoliko primjena koje spadaju u tu skupinu. Više-instrukcija-više-podataka (MIMD – Multiple Instruction Multiple Data) programa su najčešći tip paralelnih programa.

Prema David A. Patterson i John L. Hennessy „Neka računala su mješavina ovih kategorija, naravno, ali ovi klasični modeli su preživjeli zato što su jednostavni, laki za razumjevanje, i daju dobru prvu aproksimaciju. Također je – možda zbog razumljivosti – najšire korištena shema.“[3]

Tipovi paralelizma

Paralelizam na razini bita (bit-level)

Od otkrića tehnologije integracije vrlo visokog stupnja (VLSI – Very Large Scale of Integration) proizvodnje računalnih čipova 1970-ih do oko 1986. godine, ubrzanje u računalnim arhitekturama je bilo predvođeno povećavanjem veličine računalne riječi (engl. word size) – količina informacija koju procesor može izvršiti po ciklusu.[12] Povećanjem širine riječi je smanjen broj instrukcija koje procesor mora izvršiti kako bi izvršio operaciju na varijabli čija je riječ veća od veličine riječi. Primjerice, postoji slučaj gdje jedan 8-bitni procesor mora zbrojiti dva 16-bitna integera. Procesor prvo mora zbrojiti donjih 8 bitova od svakog integera korištenjem standardnih instrukcija zbrajanja, onda dodati 8 viših bitova korištenjem instrukcije zbrajanja s prijenosom i prijenosnog bita od donjih 8 bitova. Tako 8-bitni procesor zahtjeva dvije instrukcije kako bi izvršio jednu operaciju, što 16-bitni procesor može izvršiti sa jednom instrukcijom.

Povijesno gledajući, 4-bitni mikroprocesori su zamijenjeni sa 8-bitnim, potom sa 16-bitnim i na kraju 32-bitnim mikroprocesorima. Ovaj trend je završen predstavljanjem 32-bitnog procesora, koji je bio standard u računarstvu opće primjene tijekom dva desetljeća - donedavno do pojave x86-64 arhitekture, kada su 64-bitni procesori postali česti.

Paralelizam na razini instrukcije

Računalni program je u osnovi slijed instrukcija koje izvršava procesor. Ove instrukcije se mogu presložiti i kombinirati u grupe koje će se izvršiti paralelno bez mijenjanja rezultata programa. To je poznato kao paralelizam na razini instrukcije. Napreci u paralelizmu na razni instrukcija su dominirali računalnom arhitekturom od sredine 1980-ih do sredine 1990-ih.[12]

Moderni procesori imaju višestadijske instrukcijske cjevovode. Svaki stadij odgovara različitoj radnji koju procesor izvršava na instrukciji u tom stadiju. Drugim riječima, procesor sa N cjevovodnih stadija može imati do N različitih instrukcija u različitim stadijima izvođenja. Kanonski primjer procesora sa cjevovodima je RISC procesor sa pet stadija: dohvaćanje instrukcije, dekodiranje, izvršavanje, pristup memoriji i zapisivanje nazad. Procesor Pentium 4 ima 35-stadijski cjevovod.

Kao dodatak paralelizmu na razini instrukcije od cjevovoda, neki procesori mogu izvršavati više od jedne instrukcije istodobno - superskalarni procesori. Instrukcije se mogu grupirati zajedno, jedino ako ne postoji podatkovna ovisnost između njih. Semafor i Tomasulov algoritam (sličan Semaforu ali koristi preimenovanje registara) su dvije najčešće tehnike implementacije izvršavanja van redoslijeda i paralelizma na razini instrukcija.

Podatkovni paralelizam

Podatkovni paralelizam je svojstven programskim petljama, koje se fokusiraju na distribuciji podataka kroz različite čvorove za obradu u svrhu paralelne obrade. „Paraleliziranje petlji često vodi do sličnih (ne nužno identičnih) operacijskih sekvenci ili funkcija izvođenih na elementima velikih podatkovnih struktura“[12]. Mnoge znanstvene i inženjerske primjene su izložene podatkovnom paralelizmu.

Petljom prenesene ovisnosti su svojstvo iterativne petlje koja ovisi o izlazu jedne ili više prethodnih petlji. Petljom prenesene ovisnosti sprečavaju paralelizaciju petlji. Dan je sljedeći pseudokod koji računa prvih nekoliko Fibonaccijevih brojeva:

1: prev2 := 0 2: prev1 := 1 3: cur := 1 4: do: 5: CUR := PREV1 + PREV2 6: PREV2 := PREV1 7: PREV1 := CUR 8: while (CUR < 10)

Ova petlja se ne može paralelizirati zato što CUR ovisi o sebi (PREV1) i PREV2 koji se računaju u svakoj iterativnoj petlji. Kako svaka iteracija ovisi o rezultatu prethodne iteracije navedeno ne može biti izračunato paralelno. Kako veličina problema raste, uobičajeno također raste i količina podatkovnog paralelizma.

Zadaćni paralelizam

Zadaćni paralelizam je svojstvo paralelnog programa koji „potpuno različite kalkulacije može izvesti na istom ili različitom skupu podataka“.[12] Ovo predstavlja suprotnost s podatkovnim paralelizmom, gdje se ista kalkulacija provodi na istim ili različitim skupovima podataka. Zadaćni paralelizam uobičajeno ne raste srazmjerno sa veličinom problema.

Hardver

Memorija i komunikacija

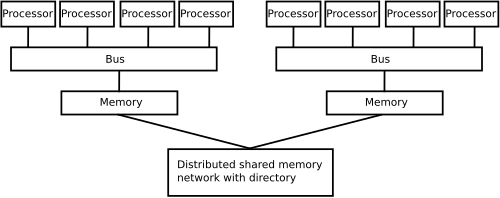

Glavna memorija u paralelnom računalu je dijeljena memorija – dijeljena među svim elementima za obradu te jednim adresnim prostorom; ili distribuirana memorija – gdje svaki element obrade ima svoj lokalni adresni prostor.[3] Distribuirana memorija se odnosi na činjenicu da je memorija logički distribuirana, ali često uključuje i to da je fizički distribuirana. Distribuirana dijeljena memorija je kombinacija dvaju pristupa, gdje procesni elementi imaju svoju lokalnu memoriju i pristup memoriji na nelokalnim procesorima. Pristup lokalnoj memoriji uobičajeno je brži od pristupa nelokalnoj memoriji.

Računalne arhitekture u kojima se cijeloj glavnoj memoriji može pristupiti jednakom latencijom i propusnošću zovemo sustavima s jednolikim pristupom memoriji (UMA - Uniform Memory Access). Uobičajeno ovo mogu ostvariti samo sustavi sa dijeljenom memorijom (gdje memorija nije fizički distribuirana). Sustavi koji nemaju opisano svojstvo zovemo arhitekturama nejednolikog pristupa memoriji (NUMA – Non-Uniform Memory Access). Sustavi sa distribuiranom memorijom imaju nejednoliki pristup memoriji.

Računalni sustavi koriste cache – male i brze memorije koje se nalaze blizu procesora i pohranjuju privremene kopije memorijskih vrijednosti (blizu u fizičkom i logičkom smislu). Paralelni računalni sustavi imaju problema sa cacheom u kojem čuvaju iste vrijednosti na više od jedne lokacije, stvarajući tako vjerojatnost neispravnog izvođenja programa. Ta računala zahtijevaju sustav usklađivanja cache, koji će paziti na spremljene vrijednosti i strateški ih čistit te osigurati ispravno izvođenje programa. „Bus snooping“ je jedna on najčešćih metoda održavanja vrijednosti kojima se pristupa (stoga ju treba čistiti). Dizajniranje velikih, brzih i cacheom usklađenih sustava predstavlja vrlo težak problem u računalnoj arhitekturi. Kao rezultat računalne arhitekture sa dijeljenom memorijom se ne skaliraju tako dobro kao i distribuirani sustavi.[3]

Procesorsko-procesorska i procesorsko-memorijska komunikacija se može implementirati u hardver na različite načine, bilo pomoću dijeljenja (bilo multiportirane ili multipleksirane) memorije, unakrsnog prespajanja (engl. crossbar switch), djeljene sabirnice ili jedne međusobno povezane mreže mnoštva topologija koje uključuju zvijezdu, prsten, stablo, hiperkocke, jake hiperkocke (hiperkocka s više od jednog procesora po čvoru), jedne n-dimenzionalne mreže itd. Paralelna računala bazirana na međusobno povezanoj mreži trebaju neku vrstu usmjeravanja kako bi se omogućilo prosljeđivanje poruka između čvorova koji nisu direktno spojeni. Komunikacijski medij između procesora velikih višeprocesorskih računala vjerojatno će biti hijerahijske topologije.

Klase paralelnih računala

Paralelna računala se mogu otprilike klasificirati ovisno o nivou u kojem hardver podržava paralelizam. To je otprilike analogno udaljenosti između osnovnih računalnih čvorova. Klasifikacije nisu međusobno isključive. Npr. klaster simetričnih multiprocesora je relativno učestao.

Višejezgrena obrada

Višejezgreni procesor je procesor koji sadrži više izvršnih jedinica (jezgri). Višejezgreni procesor se razlikuje od superskalarnog procesora po tome što superskalarni procesor može izvršavati više instrukcija po ciklusu iz jednog slijeda (niti), dok višejezgreni procesor može izvršavati više instrukcija po ciklusu iz različitih instrukcijskih sljedova. Svaka jezgra u višejezgrenom procesoru također potencijalno može biti superskalarna – na svakom ciklusu svaka jezgra može izvršavati više instrukcija iz jednog instrukcijskog slijeda.

Simultana višenitnost (od kojih je najpoznatija Intelova HyperThreading) rani je oblik pseudo višejezgrenosti. Procesor koji može imati više simultanih niti, a ima samo jednu izvršnu jedinicu („jezgru“), u vremenu kad je izvršna jedinica besposlena (kao što je promašaj cachea), koristi izvršnu jedinicu za obradu druge niti.

Intelove Core i Core 2 obitelji procesora su prve prave Intelove višejezgrene arhitekture. IBM-ov Cell mikroprocesor, dizajniran za korištenje u Sony Playstation 3 drugi je istaknuti višejezgreni procesor.

Simetrično multiprocesiranje

Simetrični multiprocesor (SMP) računalni je sustav s više identičnih procesora koji djele memoriju i spajaju se na sabirnicu. Sabirnička komunikacija ograničava sabirničke arhitekture od skaliranja. Rezultat je da SMP-ovi općenito ne prelaze 32 procesora. „Zbog male veličine procesora i značajne uštede na zahtjevima na sabirničkoj propusnosti postignutu velikim cacheom, takvi simetrički višeprocesorski sustavi su ekstremno rentabilni te pružaju dovoljnu propusnost memorijske sabirnice“.[5]

Distribuirano procesiranje

Distribuirano računalo je višeprocesorski računalni sustav sa raspodijeljenom memorijom, gdje su procesni elementi spojeni preko mreže. Distribuirana računala su visoko skalabilna.

Cluster procesiranje

Cluster je grupa slabo vezanih računala koja rade blisko zajedno pa se po mnogim karakteristikama mogu promatrati kao jedno računalo. Clusteri su sastavljeni od više samostojećih računala spojenih preko mreže. Dok računala u klasteru ne moraju biti simetrična, balansiranje opterećenja je mnogo teže kada su nesimetrična. Najčešći tip clustera je Beowulf cluster - cluster implementiran na više identičnih komercijalnih računala, spojenih preko TCP/IP Ethernet lokalne mreže. Tehnologiju Beowulf razvili su Thomas Sterling i Donald Becker. Velika većina TOP500 superračunala upravo su clusteri.

Masivna paralelna obrada

Masivni paralelni procesor (MPP) je jedno računalo s vrlo velikim brojem umreženih procesora. MPP ima mnogo istih karakteristika kao cluster, ali je uobičajeno veći te ima mnogo više od 100 procesora. U jednom MPP-u „svaki CPU ima svoju vlastitu memoriju i kopiju operativnog sustava i aplikacija. Svaki podsustav komunicira sa drugim preko brzog povezivanja“.[14]

Blue Gene/L, najbrže superračunalo na svijetu prema TOP500 rangiranju je MPP.

Grid obrada

Grid obrada predstavlja najdistribuiraniji oblik paralelne obrade. Za rad na problemu grid obrada koristi računala kilometrima udaljena, spojena pomoću Interneta. Zbog niske propusnosti i ekstremno visokih latencija na Internetu, tipična grid obrada se bavi samo sa zbunjujućim paralelnim problemima. Napisane su mnoge grid aplikacije od kojih su SETI@home i Folding@Home najpoznatiji primjeri. Najviše primjena grid obrade koriste međuprogram (middleware) – softver koji radi između operativnog sustava i aplikacija, a upravlja mrežnim resursima te standardizira softverska sučelja aplikacija za grid obradu. Najkorišteniji međuprogram za grid obradu je „Berkley Open Infrastructure for Network Computing“ (BOINC). Često, softver za grid obradu koristi „odbačene cikluse“, izvršavajući obradu dok je računalo besposleno.

Specijalizirana paralelna računala

Unutar paralelne obrade postoje paralelni uređaji za koje postoji malo interesa. Iako nisu specifični po domeni koju pokrivaju, oni su primjenjivi samo na nekoliko klasa paralelnih problema.

Rekonfigurabilna obrada s FPGA

Rekonfigurabilna obrada predstavlja primjenu FPGA kao koprocesora za računalo opće namjene. Jedan FPGA je računalni čip s mogućnosti autonomnog prežičavanja za dani zadatak. FPGA-ovi se mogu programirati s jezicima za opis hardvera kao što su VHDL ili Verilog. Ipak, programiranje u tim jezicima može biti naporno. Brojni isporučitelji su stvorili pretvorbu C jezika u HDL jezike, koji pokušavaju emulirati sintaksu i semantiku C programskog jezika koja je bliska većini programera. Najpoznatije pretvorbe C-a u HDL jezike su Mitrion-C, Impulse C, DIME-C i Handel-C.

AMD-ova odluka da otvori HyperTransport tehnologiju neovisnim proizvođačima je omogućila tehnologiju rekonfigurabilne obrade velikih performansi. Prema Michael R. D'Amour (CEO DRC Computer Corporation): „ Kad smo prvi puta ušli u AMD, zvali su nas kradljivci podnožja, a sada nas zovu svojim partnerima.“

GPGPU s grafičkim procesnim jedinicama

Obrada opće namjene na grafičkim procesnim jedinicama (GPGPU) je prilično novi trend u istraživanjima računalnih inženjera. GPU-i su visoko optimizirani koprocesori za obradu računalne grafike.[13] Obrada računalne grafike je područje u kojem dominiraju paralelne podatkovne operacije – točnije, matrične operacije linearne algebre.

CUDA je GPGPU programski jezik. CUDA je razvila nVidia za svoje grafičke kartice. CTM - Close to Metal je AMD/ATI-jevo GPGPU aplikacijsko programsko sučelje. Drugi GPU-programski jezici su BrookGPU, PeakStream i RapidMind. nVidia Tesla je nVidijina prva namjenska GPGPU kartica.

Specifični namjenski integrirani krugovi (ASIC )

Izvedeni su brojni pristupi specifičnim namjenskim integriranim krugovima (ASIC) u svrhu ovladavanja paralelnim primjenama.[14]

Zbog toga što je ASIC po definiciji posebno definiran za danu primjenu, on za nju u potpunosti može biti optimiziran. Kao rezultat, za danu primjenu ASIC nastoji po performansama dostići računala opće namjene. Ipak, ASIC se izrađuje litografijom X-zraka. Ovaj proces zahtjeva masku koja može biti vrlo skupa. Jedna maska može koštati više od milijun američkih dolara. Što je manji tranzistor koji čip koristi to će biti skuplja maska. Međutim, rast performansi u obradi opće namjene kao rezultat Mooreovog zakona nastoji izbrisati te napretke u jednoj ili dvije generacije čipova. Tako visoki početni troškovi i sklonost dostizanja obrade opće namjene koju vodi Mooreov zakon, čini ASIC nemogućim za većinu primjena paralelne obrade.

Vektorski procesori

Vektorski procesor je CPU ili računalni sustav koji može izvršavati iste instrukcije na velikim skupovima podataka. „Vektorski procesor ima operacije visokog nivoa koje rade s linearnim nizovima brojeva ili vektora. Primjer vektorske operacije je A=B ×C, gdje A, B i C čine svaki 64-elementni vektor 64-bitnih brojeva s pomičnim zarezom. Usko su povezani s Flynnovom SIMD klasifikacijom. Cray računala su postala slavna zbog svojih računala za vektorsku obradu 70-ih i 80-ih godinama prošlog stoljeća. Ipak, vektorski procesori – ujedno CPU-i i potpuni računalni sustavi – općenito su nestali. Moderni procesorski instrukcijski setovi uključuju neke instrukcije za vektorsku obradu, kao što su AltiVec i SSE (Streaming SIMD Extensions).

Softver

Paralelni programski jezici

Brojni konkurentni programski jezici, biblioteke, API-i i paralelni programski modeli su stvoreni za programiranje paralelnih računala. Ona se općenito mogu podijeliti u skupine bazirane na pretpostavci o memorijskoj arhitekturi – dijeljena memorija, distribuirana memorija ili dijeljeno-distribuirana memorija. Programski jezici za rad s dijeljenom memorijom komuniciraju upravljanjem dijeljenih memorijskih varijabli. Distribuirana memorija koristi sustav poruka. POSIX Threads i OpenMP su dva najraširenija korištena API-a za dijeljenu memoriju, gdje je Message Passing Interface (MPI) najrašireniji sustav prosljeđivanja poruka. Jedan od koncepata koji se koristi kod programiranja paralelnih programa jest koncept budućnosti, gdje se u budućnosti jedan dio programa obvezuje proslijediti traženi podatak drugom dijelu programa.

Automatska paralelizacija

Automatska paralelizacija sekvencijalnih programa je „sveti gral“ paralelne obrade. Usprkos desetljećima rada istraživača kompajlera, automatska paralelizacija je imala samo ograničeni uspjeh. Matični paralelni programski jezici ostaju ili izričito paralelni ili u najboljem slučaju djelomično bezuvjetni, u kojima programer kompajleru daje direktivu za paralelizaciju. Postoji nekoliko potpuno bezuvjetnih programskih jezika - SISAL, Parallel Haskel i (za FPGA) Mitron-C no oni su jezici koji se gotovo ne koriste i nisu široko rasprostranjeni.

Aplikacijsko izjednačavanje (checkpointing)

Što je računalo veće i složenije, više stvari može poći po zlu i kraće je srednje vrijeme između kvarova (MTBF). Aplikacijsko izjednačavanje je tehnika gdje računalni sustav uzima „snimku stanja“ aplikacije – zapis svih trenutnih područja resursa i stanja varijabli, srodno središnjem skladištu. Ova informacija se može iskoristiti za povrat programa u slučaju kvara na računalu. Aplikacijsko izjednačavanje znači povrat programa na zadnji checkpoint, a ne na početak. To je presudno za aplikaciju koja se izvršava mjesecima. Aplikacijsko izjednačavanje može olakšati migraciju procesa.

Primjena

Kako su paralelna računala postajala veća i brža, postajala su sposobnija rješavanju problema čija su rješenja prije bila nedostižna. Paralelna obrada se koristi u širokom spektru primjena, od bioinformatike (slaganje proteina) do ekonomije (simuliranja matematičkih financija). Česti tipovi problema koji se nalaze u primjenama paralelne obrade su[2]: - Gusta linearna algebra, - Rijetka linearna algebra, - spektarne metode (kao što su Cooley-Tukey brza Fourierova transformacija), - N-body problemi (kao što su Barnes-Hutova simulacija), - Strukturirani grid problemi (kao što je KLattice Boltzmannova metoda), - Nestrukturirani grid problemi (kao što se nalaze u analizi konačnih elemenata), - Monte Carlo simulacije, - Kombinacijska logika (kao što su brute-force kriptografske tehnike), - Traversali na grafu (kao što su algoritmi pretraživanja), - Dinamičko programiranje, - Metode grananja i ograničavanja, - Grafički modeli (kao što je traženje Skrivenih Markovih modela i konstruiranje Bayesovih mreža), - Simulaciji stroja sa konačnim brojem stanja.

Povijest paralelnih arhitektura

Porijeklo pravog (MIMD) paralelizma ide nazad do Federica Luigia, Conte Menabrea i njegovog „Nacrta Analitičkog stroja kojeg je izmislio Charles Babbage“. IBM je 1954. godine predstavio 704, kroz projekt čiji je glavni principijelni arhitekt bio Gene Amdahl. To je bilo prvo komercijalno dobavljivo računalo koje je koristilo potpuno automatske aritmetičke naredbe za brojeve sa pomičnim zarezom. 1958. godine IBM-ovi istraživači John Cocke i Daniel Slotnick su prvi raspravljali o korištenju paralelizma u numeričkim računima. Burroughs Corporation je 1962. godine predstavila D825 - četiri procesorsko računalo koje ima 16 memorijskih modula s unakrsnim preklapanjem. 1967. godine Amdahl i Slotnick su objavili raspravu o izvedivosti paralelne obrade na konferenciji Američke federacije društava za Obradu informacija. U toj raspravi Amdahl je postavio svoj zakon koji definira maksimalno ubrzavanje zbog paralelizma.

1969. godine, američka kompanija Honeywell je predstavila svoj prvi Multics sustav - simetrični multiprocesorski sustav s mogućnošću rada do osam paralelnih procesora. Višeprocesorski projekt C.mmp iz 1970. godine, razvijen na Carnegie Mellon Sveučilištu predstavlja „jedan od prvih multiprocesora sa više od nekoliko procesora.“ „Prvi sabirnicom spojeni višeprocesorski sustav s dijeljenim cacheom bio je Synapse N+1 iz 1984. godine.“

SIMD paralelna računala su nastala 1970-ih godina. Motivacija razvoja navedenih SIMD računalnih sustava je bila amortizacija kašnjenja logičkog sklopa procesorske kontrolne jedinice pomoću više instrukcija. Slotnick je 1964. godine predložio izgradnju masivnog paralelnog računala za Lawrence Livemore National Laboratory. Njegov dizajn je financiran od strane američkih zračnih snaga, iz čega je nastalo najranije SIMD paralelno računalo ILLIAC IV. Ključ njegova dizajna je bio prilično veliki nivo paralelizma, do 256 procesora, što je dozvolilo računalu rad s velikim skupovima podataka, što je kasnije nazvano vektorskom obradom. Ipak, ILIAC IV je ostao poznat kao „najsramotnije superračunalo“ zato što je završen samo do četvrtine, ali je trajao 11 godina i koštao gotovo četiri puta više od osnovne procjene. Kada je 1976. godine napokon bilo spremno za izvršavanje svoje prve stvarne aplikacije, nadmašeno je od postojećih superračunala kao što je Cray-1.

Izvori

- ↑ G.S. Almasi and A. Gottlieb. Highly Parallel Computing. Benjamin-Cummings publishers, Redwood city, CA, 1989.

- ↑ Krste Asanovic et al. The Landscape of Parallel Computing Research: A View from Berkeley (PDF). University of California, Berkeley. Technical Report No. UCB/EECS-2006-183. 18. prosinca, 2006.: "Stara [dogovoren pogled]: Povećanje frekvencije takta je osnovna metoda poboljšanja performansi procesora. Nova[dogovoren pogled]: Povećanje paralelizma je osnovna metoda za poboljšanje performansi procesora ... Čak i predstavnici Intela, kompanije koja se općenito vezala za hipotezu "viši takt znači brže izvođenje", proglasila je da tradicionalni pristup povećanja performansi putem povećanja takta dosegao svoj maksimum."

- ↑ Asanovic et al. Stara [dogovoren pogled]: Snaga je besplatna, ali tranzistori su skupi. Nova [dogovoren pogled] je [da] je snaga skupa, ali su tranzistori "besplatni".

- ↑ David A. Patterson i John L. Hennessy. Computer Organization and Design (Drugo izdanje) Morgan Kaufmann Publishers, 1998. ISBN 1558604286, p. 715.

- ↑ 5,0 5,1 Introduction to Parallel Computing. Lawrence Livermore National Laboratory 0. 9. studenoga 2007 1.

- ↑ John L. Hennessy i David A. Patterson. Computer Architecture: A Quantitative Approach. 3rd edition, 2002. Morgan Kaufmann, ISBN 1558607242, p. 43.

- ↑ J.M. Rabaey. Digital Integrated Circuits. Prentice Hall, 1996. ISBN 0131786091, p. 235.

- ↑ Laurie J. Flynn. Intel Halts Development of 2 New Microprocessors. The New York Times, 8. svibnja, 2004. Otkriveno 22. travnja, 2008.

- ↑ G. Amdahl. The validity of the single processor approach to achieving large-scale computing capabilities. In Proceedings of AFIPS Spring Joint Computer Conference, pp. 483–85, Atlantic City, N.J., April 1967. AFIPS Press.

- ↑ The Mythical Man-Month: Essays on Software Engineering. Frederick P. Brooks Jr.. Chapter 2 - The Mythical Man Month. ISBN 0201835959

- ↑ Reevaluating Amdahl's Law Communications of the ACM 31(5), 1988. pp. 532–33.

- ↑ A.J. Bernstein, "Program Analysis for Parallel Processing,' IEEE Trans. on Electronic Computers, EC-15, listopad 1966., pp. 757–62.

- ↑ Roosta, Seyed H. Parallel processing and parallel algorithms: theory and computation. 2000. Springer, ISBN 0387987169, p. 114.

- ↑ MPP definicija. PC Magazine. Otkriveno 7. studenog, 2007.